# A low cost implementation of a dual-stage interleaved bidirectional boost converter

THUAS Delft, The Netherlands F.M. Boendermaker, D.C. Zuidervliet, P.J. van Duijsen(presenter)

www.dc-lab.org

July 20-22, 2022

#### Table of contents

- Introduction

- Question

- Comparison

- Boost overview

- System overview

- Control Circuit design

- Simulation and Validation

- PCB set up

- Conclusions

#### Question

#### Bidirectional from 48volt to 350volt

- Easy construction

- Cost efficient

- Simple control

- Fault tolerant

### Comparison

#### Bidirectional from 48volt to 350volt

- Boost, impossible with feasible dutycycle!

- Synchronous Buck-Boost, impossible with feasible dutycycle!

- Quadratic converter, Bidirectional is possible?

- Full Bridge, Bidirectional is already a DAB!

- DAB: Dual Active Bridge, expensive coupled inductors

- Multiple stage boost converter, but how many?

- Dual Stage interleaved boost converter, CONSIDERED!

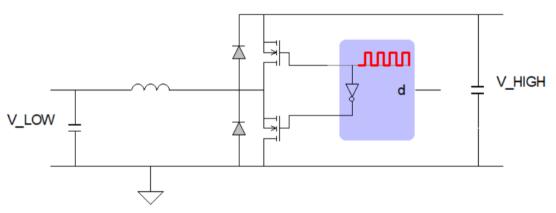

#### **Boost overview**

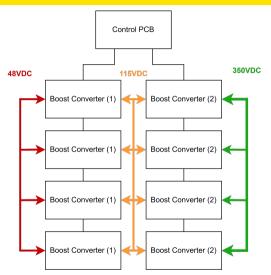

#### Two-Stage Dual Boost converter

- Minimum of components

- Interleaved parallel

- Reduce Ripple

- Pault tolerant

- Optimize efficiency by selecting number of parallel converters

- Less semiconductors compared to the DAB

- Only two single inductors, no coupled inductors

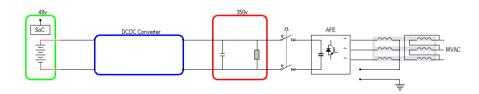

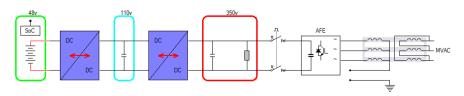

# System overview

System overview of the two-stage interleaved boost topology.

Bidirectional synchronous buck converter is the same as a boost converter

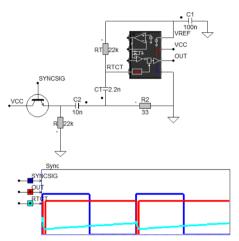

# Synchronizing Interleaved

Synchronisation. The Dark blue signal is the clock the UC3843is synchronized to. The red signal is the output of the UC3843. The cyan waveform is the voltage on the RT/CT pin.

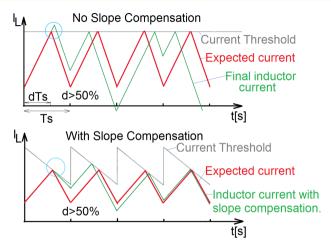

# Slope Compensation circuit

Slope compensation circuit,  $R_{Ramp}$  defines the slope compensation current.

# Slope compensation waveforms

Slope compensation visualisation, reducing the current threshold by increasing the the measured current with an extra slope through  $R_{RAMP}$ .

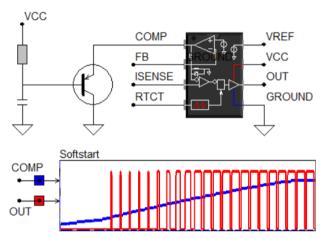

Softstart. The blue signal is the voltage on the COMP pin, the red waveform is the UC3843 output.

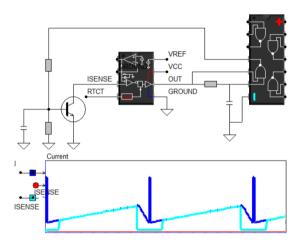

### Leading edge blanking

Leading Edge Blanking. The dark blue waveform represents the voltage directly on the shunt. The cyan waveform is thevoltage directly on the ISENSE pin.

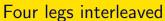

Simulation of four legs working interleaved. The top waveform shows the input current. The other waveforms are the individual inductor currents per converter.

# **Dual-stage simulation**

Simulation of two stages. The dark blue line represents the output voltage of the first stage, the red line shows the output voltage of the second stage.

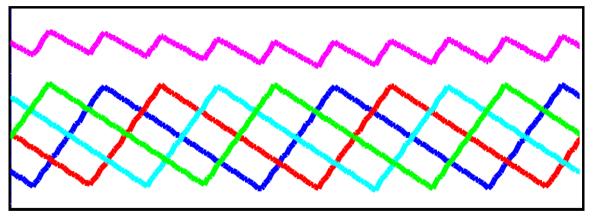

#### Measurement result

Scope image of test setup. CH1 = Vout, CH2 = UC3843 Output, CH3 = Voltage on Isense pin, CH4 = Voltage over Shunt.

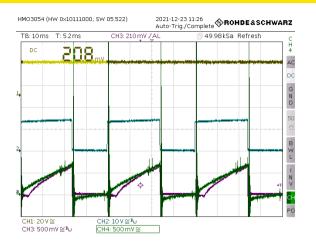

#### Stacked concept

Concept 3D model of multiple prints stacked and connected using four busbars, (Ground, 48v, 115v and 350v).

- Interleaved Dual-Stage Boost

- Stacked modular construction, cost efficient

- Optimize efficiency, by selecting number of parallel converters

- Fault tolerant

# Thank you! www.dc-lab.org